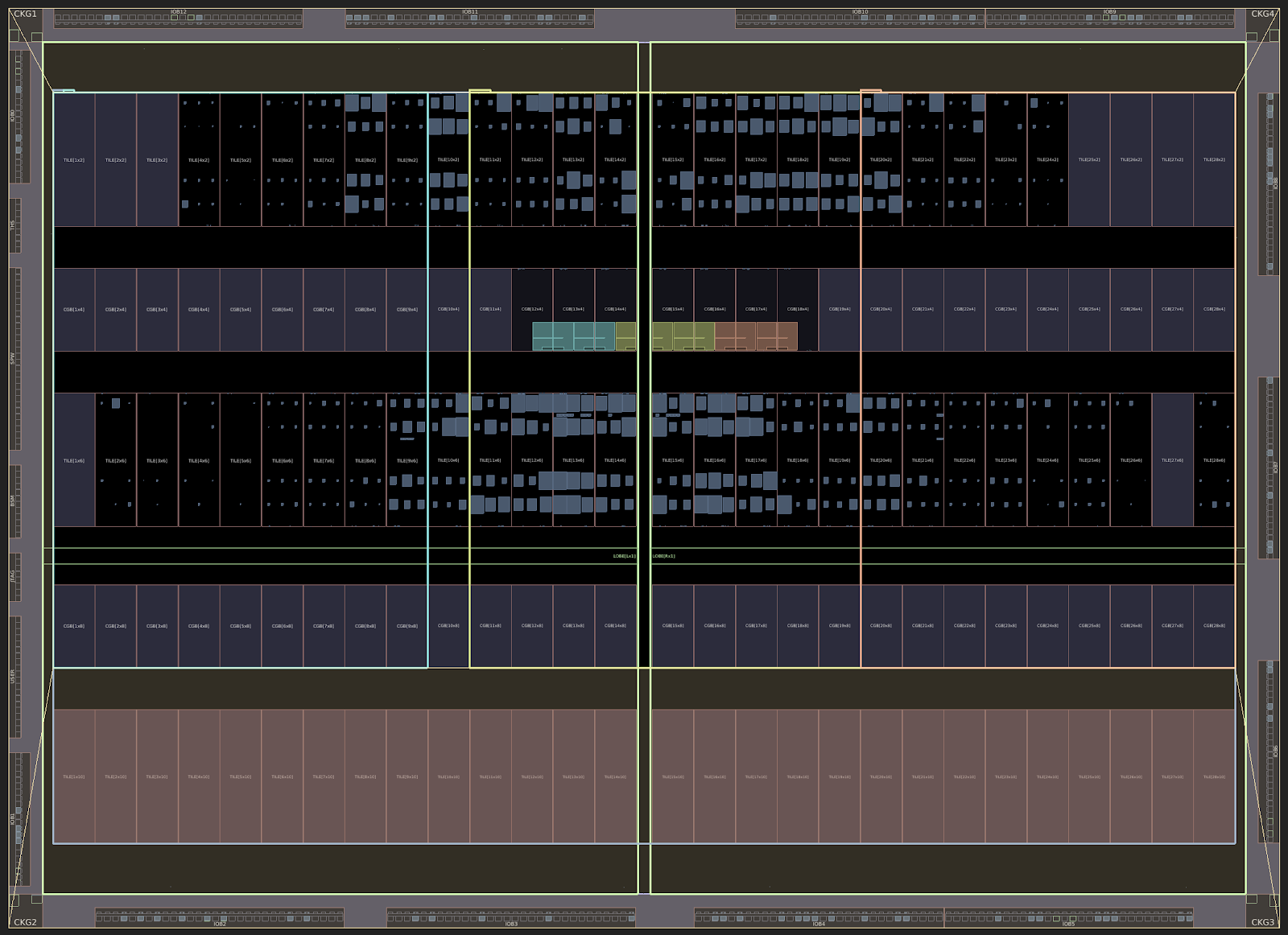

NX developed 120 benchmarks to run a benchmark analysis. Following this analysis, NX has been able to significantly improve the overall results of NXMAP. NX has also demonstrated the possibly to reach more than 80% utilization rate on NG-MEDIUM. All production tests are now based on NXMAP, illustrated by the following design testing all embedded memories. A lot of improvement has been done on NXMAP:

Timing raised by 5-30 %

Run time reduced by 5 in average

Memory consumption reduced by 4 in average

NX developed different IPs available on a tool called NXCore (APB slave to SPW configuration, NXScope, SER/DES, Systolic, Transpose Symmetric, DDR2 DFI, Asynchronous FIFO). NXCore is a platform developed by NX to download all available IPs to be used on its FPGA.

NX has done the preparation of the test vehicle for the two radiative test campaigns done at UCL with ESA and CNES. The two first test campaign confirmed the robustness of NG-MEDIUM:

The configuration SER is divided by 9400 comparing to the unhardened structure.

The CMIC failure/uncorrected double error cross-section at 62.5 MeV.cm²/mg is more than 1 decade below the SEU cross-section.

The contribution of DPRAM uncorrected MBU, SEFI, DFF SEU with clock SET or the toggle DFF error (24MHz) to chip SER is negligible compared to the one of configuration memory.

By replacing the layout of 4 config, the average configuration bit SER will be divided by more than 33 to 8.26E-13 SEU/bit/day. Since NG-LARGE capacity will be 4 times bigger, the chip will have less than one error every 130 year.

NanoXplore has coordinated the project and supported the partners in the consortium.

ST Microelectronics has been in charge of the qualification of the NG-MEDIUM device.

The successful qualification ensures the device is adequate and suitable to be used in space missions without any additional analysis, and with cost and lead time efficiency.

This is essential to penetrate the space market, and puts the NG-MEDIUM on par with other non-european FPGA devices in terms of readiness for new space missions, but with the extra availability provided by the non-dependency on entities outside europe and the lack of any import restrictions.

The new product qualification plan defined in accordance with MIL-PRF-38535L and ESCC 2269000 has been conducted for Screening, Group A, B, C, D and E (SEE / SEL performed through CLGA package). It has been performed for Sreening, Group A, B, C, D and E (SEE/SEL).

The different groups of tests are summarized here:

Group A (electrical tests): static, dynamic, functional and switching tests at +25ºC, maximum and minimum rated operating temperatures.

Group B (mechanical and environment tests): Resistance to solvents, Bond strength, Shear tests, Solderability.

Group C (life tests): Steady-state life test, End-point electrical parameters.

Group D (package related tests): Physical dimensions, Lead integrity, Shear/Pull tests, Thermal shock, Temperature Cycling, Moisture Resistance, End-point electrical parameters, Mechanical shock, Vibration, Acceleration, Salt atmosphere, Internal tests, Adhesion tests, Lid torque, Soldering heat.

Group E (radiation testing): Single Event Upset (SEE), Single Event Latchup (SEL), Total Ionizing Dose (TID)

Concerning Group C, failure observed during the first qualification campaign on die cut 1.0 after 2000 hrs Electrical Test read-out has been successfully corrected through the die cut 1.1; indeed, no failure has been reported during the life test 2000 hrs performed.

The QML-V qualification exercise performed on NG-MEDIUM FPGA encapsulated in a CQFP352 package is considered PASS for Screening, Group A, B, C and E (SEE/SEL). Group D and E (TID) will be considered PASS providing that TID performed on CLGA package, and analysis on the 2 remaning samples under analysis in Group D are successful.

QML-V Test |

Conditions |

IN |

OUT |

Comments |

Manufacturing & Screening |

- |

92 |

78 |

14 |

Group A |

In

accordance with SMD In

accordance with SMD In

accordance with SMD |

70 |

69 |

PASS SN #05 damaged by handling issue before submission @ Tc= -55°C |

Group B |

- |

4 |

4 |

PASS |

Group C |

Life Test 2000 hours @ Tj= +125°C |

22 |

22 |

PASS |

Group D |

- |

51 |

51 |

PASS |

Group E |

SEE

/ SEL Tests as per |

4 |

4 |

PASS |

Group E |

TID |

11 |

|

On going |

To fully comply with the ESCC 2269000, some additional tests need to be performed. Tests in Group 2 SG #2d correspond to additional mechanical and thermal vacuum tests:

Conditions |

IN |

OUT |

Comments |

|

Group 2 SG #2d |

Thermal route |

10 |

10 |

PASS |

Group 2 SG #2d |

Mechanical route |

10 |

10 |

PASS |

Construction Analysis |

DSO/AQ/LE-2019.0017189 report |

3 |

3 |

Recommendations provided to improve Sealing Process |

Thales Alenia Space - España (Spain) has been in charge of coordinating the Radiation Evaluation & Mitigation work package of the project.

TAS-E has also developed the Test Vehicle PCB board that has been used in the radiation experiments.

TASinS has been involved in two main working packages:

WP1: FPGA Validation

TASinS has participated as end-user on the functional testing and review of the general design flow and device.

WP2: Radiation evaluation and mitigation

TASinS as Working Package Leader has been reponsible for the performance and reporting of Radiation tests both for TID and SEE.

TASinS has performed extensive evaluation activities of the NanoXplore BRAVE FPGA and NanoXmap tool chain.

The main goal of the activity has been to analyze the NanoXmap tool behavior throughout the different stages of a typical FPGA design flow, from VHDL capture and simulation, passing to Synthesis and Place& Route stages, down to postlayout Static Timing Analysis and logic level simulation and FPGA programming.

It must be pointed out that the Brave FPGA tool chain has been evaluated for several versions of the tool up to release 2.8.3. Furthermore, different designs have been loaded on the Evaluation Board and functionally tested. Moreover, resource utilization and maximum working frequencies have been analyzed.

TASinS with the support of Nanoxplore, has performed several heavy ions testing campaigns in order to characterize the device not only in SEL, but also in Configuration Memory SEU, Dynamic SEU and SEFI

The radiation tests were performed at the Cyclotron Resource Centre located in the Université Catholique de Louvain (UCL) at Louvain-la-Neuve, Belgium.

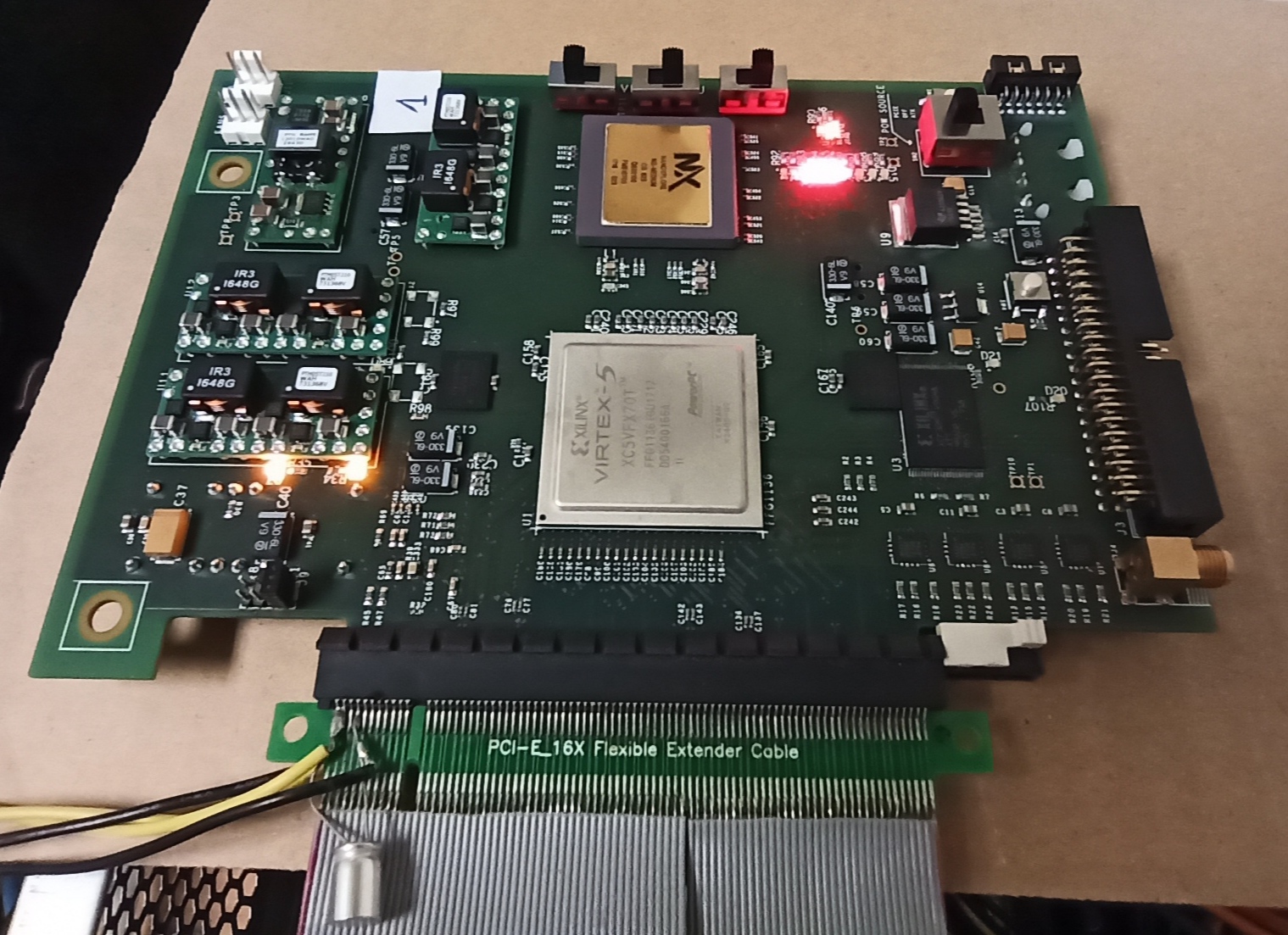

The test hardware used for these campaigns was composed of two boards:

A control board, used as a base board and supporting the control, supply and interface hardware.

A mezzanine board supporting the device to be tested.

Fig. 1- Test Board Picture

The control board is connected through USB to the host computer, and uses a single 12V main power supply. It is built around a Cypress EzUsb microcontroller and a companion FPGA (Spartan 6SLX25), and integrates:

Its own power supplies from main +12V.

Four latch up protected power supplies modules providing four target supply rails.

Power supplies voltage and current measurement instrumentation.

Control for heaters to raise device temperature.

However, for the DUT’s power supply, and latch up and temperature control, the CLARK 1 was used.

TAS-E has developed a fully automated Latch-up control system (CLARK 1) capable of testing up to 18 individual components in one run, featuring individual heating of components up to 150ºC, individual current monitoring and 3 different digitally adjustable power rails from -30V to +30V for each individual component. It also allows the testing of more complex systems such as Electrical Models boards and Evaluation boards

The control application used is the one provided by NanoXplore. The hardware is connected by a USB 2.0 link to a control PC running the application software. This software is developed with the Python language with USB, QT4 and matplotlib packages.

The software includes:

A graphical User Interface.

An API to control the power supplies. (Performed using CLARK 1)

An API to control and monitor the power currents. (Performed using CLARK 1)

An API to control the device temperature. (Performed using CLARK 1)

An API to access the FPGA block.

An API to control the ion beam shutter.

The test software is launched by the graphical interface and calls API functions to:

Download patterns in the configuration memory.

Open and close the beam shutter.

Read back the configuration memory.

Store and correct potential SEU.

Delidding of the chip was done in order to directly irradiate the die.

Radiation tests were performed at the Cyclotron Resource Centre located in the Université Catholique de Louvain (UCL) at Louvain-la-Neuve, Belgium.

Their Heavy Ion Irradiation Facility ( HIF ) was used for the testing.

Fig. 2- UCL HIF Equipment

The radiation tests were performed with the following ions:

Table 1. High Penetration Ions

M/Q |

Ion |

LET |

DUT energy |

Range |

[MeV/mg/cm²] |

[MeV] |

[µm Si] |

||

3.14 |

22 Ne 7+ |

3.3 |

238 |

202.0 |

3.33 |

40 Ar 12+ |

10.0 |

379 |

120.5 |

3.35 |

84 Kr 25+ |

32.4 |

769 |

94.2 |

3.32 |

103Rh31+ |

45.8 |

972 |

88.7 |

3.54 |

124 Xe 35+ |

62.5 |

995 |

73.1 |

The beam flux is variable between a few particles/s.cm2 and 104 particles/s.cm2. The beam flux can be modified from the user station, this is done with injection grids (for a constant attenuation factor) or by inflector bias variations (for intermediates values). The Homogeneity is ± 10 % on a 25 mm diameter.

As part of TID testing Activities, TASinS designed and manufactured two test boards, each of them with the capability to allocate up to six DUTS in CG625 package.

Fig. 3- TID Irradiation Board

The testing board allows:

External Power supply monitoring during irradiation.

FPGA self-configuration through SPI Flash memory.

FPGA Visual Health-check by using dedicated visual indicators.

TID testing campaign was perfomed in TRAD in Toulouse up to a Total Dose of 100Krad.

TAS-F has mainly worked on the evaluation of NanoXmap V2 by comparing the performances of NG-MEDIUM FPGA with other targets.

Resource utilization results are encouraging compared to other technologies. Indeed, the NanoXmap synthesis process seems to be as efficient or more to be made. At the end of the flow, too many functional elements are used. A lot of LUT are used in order to route other instances (DFF, CY, RF, etc.). Then, most of the time, the placing process fails when the percentage of functional element reaches 75% - regarding the tested designs during this evaluation timeframe. Finally, a RTAX2000 design mostly fits into a NG-MEDIUM device.

Process time is a bit longer than some other tool set. Hence, this is a slight difference for design over 50% occupancy of the NG-MEDIUM.

Concerning static timing analysis, overall reached frequency is not really high. However, results on these designs may be improved with future NanoXmap versions. Indeed, the static timing analyzer is not optimized and the timing constraints do not really seem to be taken into account.

Thales Alenia Space - France has also worked on the validation of hardware features in the FPGA.

Different versions of NanoXmap released between nov. 2016 and august 2018 have been tested on different types of designs. Performances of the synthesis were good and equivalent to results obtained from the synthesis tools of other FPGA vendors.

Some testcases showed some limitations in the Place & Route tool that was using too many LUTs for routing and then degrading area and timing performances. The testcases have been shared with NX so the tool could be improved.

IOs and Memory have been successfully tested on the NG DevKit electronic board.

ADS Tres Cantos has worked on porting actual VHDL designs, into the new BRAVE-Medium FPGA target device, and on the CGA625 assembly validation report to demonstrate the readiness for using VEGAS CGA 625 packages.

Results of work done on SpaceWire Driver VHDL

The SpaceWire driver was synthesized, and a layout was done on the NG-Medium FPGA. The tool used to do the layout in the NG-Medium FPGA was NanoXmap and NanoXpython tools. The design was checked on actual NG-Medium FPGA on the NX prototyping board. Communications between SpW drivers were checked externally by the controlling PC.

It was checked on actual HW that the SpW drivers were able to establish connections to talk to each other at 10Mbps, and 50Mbps, however, no higher frequency was possible to obtain, due to issues with the controllability of the synthesis and layout process with the current tools.

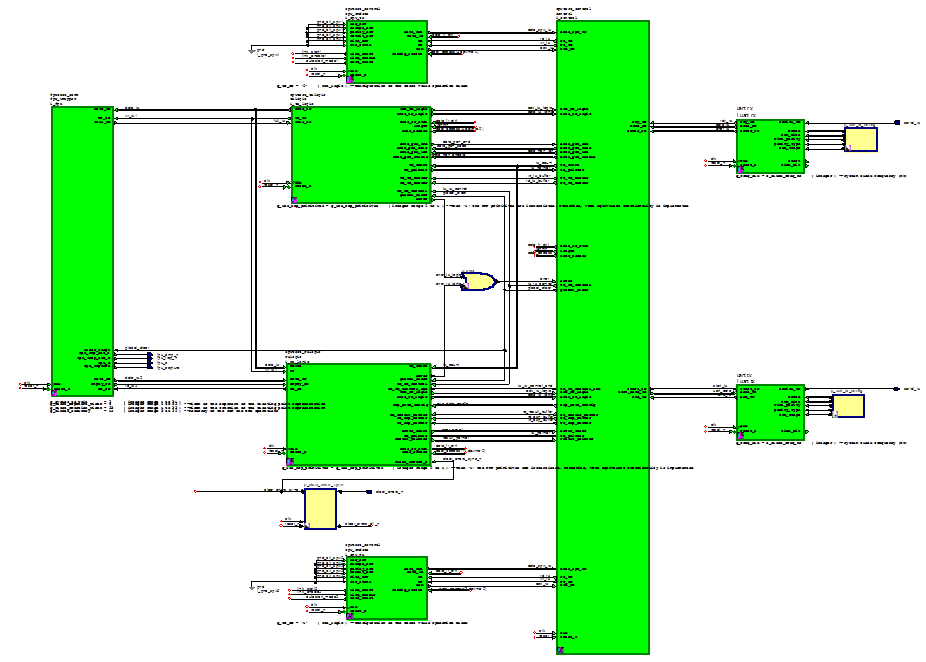

Figure 1, HW Setup and NX Evaluation Board.

Results of work done on Floating Point Unit VHDL

The Floating Point Unit was synthesized, and a layout was done on the NG-Medium FPGA. The tool used to do the layout in the NG-Medium FPGA was NanoXmap and NanoXpython tools. The design was checked on actual NG-Medium FPGA on the NX prototyping board

The timing of the generated layout was checked by doing Static Timing Analysis, and the functionality of the produced layout was checked by exporting a gate-level netlist with timing back-annotation that was simulated afterwards with Questasim.

Figure 2, VHDL Setup with FPU instantiation

In the HW, the FPU was commanded to operate on a set of operands preprogrammed by the controlling PC. It was checked that the FPU performed well all operations, and the operation results were as expected.

Results on Package Assembly Activities:

ADS Tres Cantos has worked on the CGA625 assembly validation report to demonstrate the readiness for using VEGAS CGA 625 packages

Assembly was done on multi-layered PCB substrates, made of Poly-imide resin, reinforced with Fiber Glass, compatible with the targeted market for space application.

Verification were done using visual inspection and micro-section technique at the end of testing campaign to check solder joints, PCBs integrity and ceramic packages.

Figure 3: CCGA 625 with Six-Sigma Columns attached (up: TOP, down: BOT)

Figure 4: CCGA 625 (SN06) assembled son SP271

This is a short summary of activities during 2018 and 2019 regarding CGA625 assembly validation

Assembly and verification of the CGA625 automatic assembly process (pitch 1mm)

Samples received from NanoExplore September 2018

Transfer to ELC together with PCB for Test Vehicles manufacturing October 2018

Phase 1/2 Manufacturing capability & Verification Program:

LGA625 column attach to get CGA at ELC 2019 Q1

CGA625 Soldering, repair (desoldering+soldering) at ELC 2019 Q1

Qualification campaign:

vibration at ELC 2019 Q1

500 thermal cycles at TCS 2019 Q2

Micro sections at ELC 2019 Q3

Validation Report ELC+TCS 2019 Q4

The aim of the activity on the ‘VEGAS Systematic FPGA function validation’ WP1 can be divided in 2 main parts.

First of all the tool suite NXmap has been tested on 2 digital signal processing algorithms. The tool version used are going from 2.8.1 to 2.9.1. The design have been synthesized, place, routed and analyzed in timing. Results in terms of resource usage were in line with the design sizes. Concerning frequency performances the tool’s given frequencies were not impacted by frequency constraints (called ‘timing driven’ algorithm). Run time of the tool suite was around 30 minutes for a design that represent 65% of the NG-MEDIUM capacity. The evolution of the tool has been significant over the versions.

Tool analysis has been performed on two specific designs. The first design is a signal processing IP optimized for RTG4. The second design is also a signal processing IP which has been synthesized in technologies such as RTG4 or RTAX2000. For theses 2 designs, the complete flow (synthesis, Place & Route, Static Timing Analysis) have been performed using NanoXmap versions 2.8.1 to 2.9.1. Different software versions have been compared, and also resource comparisons as well as frequency comparisons with other FPGA have been done. The run time of the tool chain was presented and compared with the requested frequency.

In a second time, the validation of the NG-MEDIUM macroblocks cells is performed on the evaluation kit board. The tested macroblock cells are the NX_FE, NX_DSP, NX_CY, NX_WFG, NX_PLL. The method applied was to perform tests on the board using all possible configuration of a single macroblock and random test vectors. The results were compared to the simulation model of the macroblocks and to a software model design using the macroblocks’ datasheet description. At the end of the tests; all results were in line with the simulation and their description in the datasheet. No errors were found in the FPGA matrix.

The features of the NG-MEDIUM have been tested using a DevKIt Version 1. Tests have been run with versions 2.8.1 to 2.9.1, all errors have been reported and corrected. The features tested in ADS-F are the DSP blocks, the PLL blocks, and logical elements such as the carry, the 4-LUT or the DFF which are provided in the NX_Library. Their behavior has been compared to the one described in documentation using a soft model and the simulation model.

Figure 1 : Test environment for NG-MEDIUM features tests

In parallel to VEGAS activity, ADS-F did a collaborative work with the NanoXplore software tools development team in order to improve the flow. All issues or bugs found have been reported and corrected. We also proposed new features to be integrated in the tools. Many exchanges have been done in this project in order to give the point of view of an end-user of the NG-MEDIUM FPGA.

Our work aim to validate the new European FPGA technology suitable for space applications and the complementary new software tools. The evaluation is performed by porting real designs to the new technology. The chosen designs are the Advanced GPS/GALILEO ASIC (AGGA-4) and three digital signal processing algorithms (FFT Radix-2 and Radix 4 and a Digital Down Converter (DDC)).

The main steps of the validation process were as follows:

Making an assessment of the portability of the selected applications into the NG-Medium FPGA

Performing all steps to port the feasible applications into the FPGA. This includes executing synthesis, place and route, running post place and route simulations tests, loading the bitstream to the device and making physical tests

Evaluating and comparing the results with already existing solutions on other FPGAs

Each stage of the work flow revealed the status of the software tools accompanying the FPGA:

The issues and learned lessons met throughout the way were carefully documented and points for improvement were suggested

Information for the performance and area utilizations of the new FPGA was gathered for each design with multiple changes of the software settings

Comparison of the results after synthesis and place and route was done against other technologies

The development of the tools during the project was monitored

The functional validation was executed with development board, which includes the NG-Medium FPGA. The board receives a 26-pin ribbon cable from NanoXplore Angie USB-JTAG interface. This interface is used to load the bitstream. NxBase2 software is used to interact with the board and upload the bit stream into the chip. JTAG connector also provides connection for read back and optional override that are controlled from NxBase2 tool. A 25 MHz clock oscillator is provided on the board. This clock is used as an FPGA clock input. For characterization tests and/or clock domain validation, a clock divider is used to generate the different clock frequencies needed.

The NG-Medium development board includes several connectors:

SpaceWire

Altera HSMC mezzanine

FMC (VITA-57)

The main goal for the validation tests was to check if the new FPGA technology was programmed correctly with the bitstream and if the real design was functioning correctly on the NG-Medium architecture. A part of the tests aims to validate that the primitives blocks (DSP, LUT, clock tree … ) of the technology behave as depicted on the documentation as on the simulation and on the board. The test environments used in Airbus Ottobrunn is shown on the fig. 1.

Fig. 1 Environment for LEON tests

Porting real designs to NG-Medium showed that the main challenges for this FPGA technology are coming from the new SW tools.

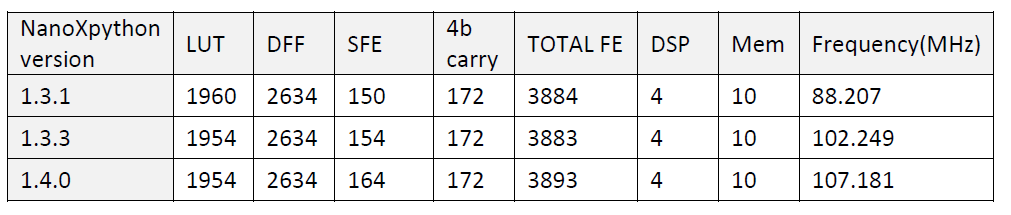

All along the project, we have noticed that the tools are constantly improved. Each version provides better performance than the previous without causing resource penalties (fig. 2).

Fig. 2 Different versions of the SW tools comparison for IFFT radix-2 (similar results for the other designs)

Post-layout simulations were performed and passed, showed that the SW tools produce working netlists.

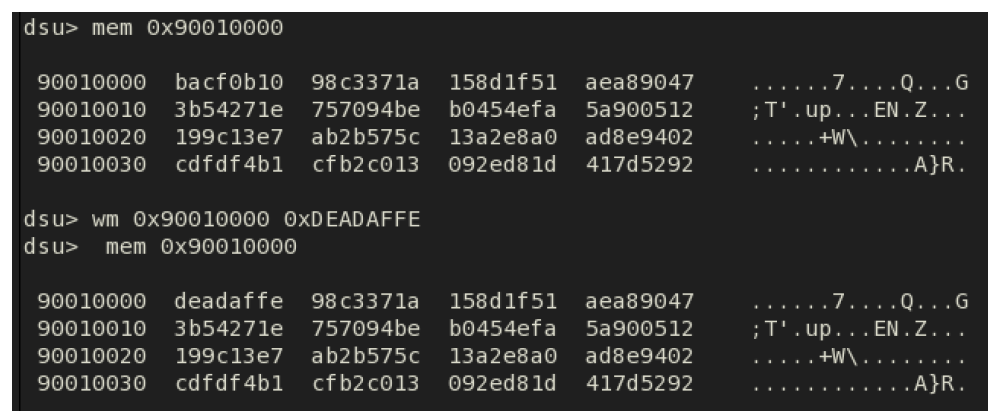

Last but not least, the technology was proven to work by successfully allowing porting of LEON2 processor to the FPGA on the development board and running simple applications as well as reading and writing to the memories and LEON registers (fig. 3) .

Fig. 3: Writing and reading the LEON registers

Deliverable WP1_D1.2:

In the frame of VEGAS an inverse FFT Radix-2 and Radix 4 and a Digital Down Converter (DDC) were tested. The VHDL code for the Radix-4, Radix-2 and Digital Down Converter were provided from another project done at Airbus. The algorithms were first developed in Matlab as Simulink block schemes and then they were automatically translated to VHDL thanks to HDL coder and HDL workflow advisor.

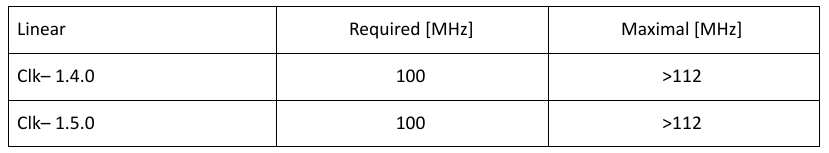

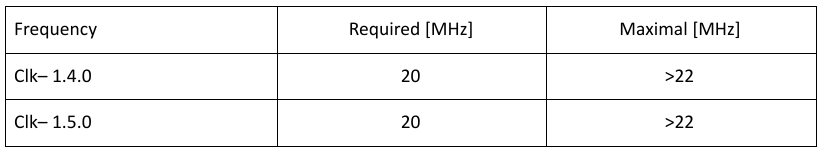

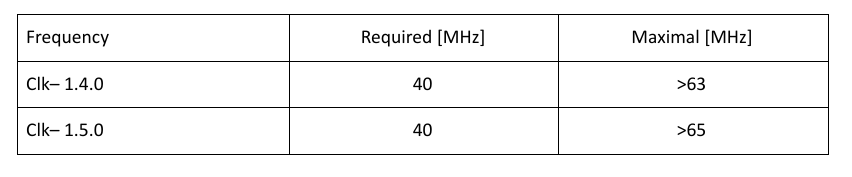

Table 1: Maximum clock speed after simulations with linear timing optimisations, comparison between NanoXPython 1.4.0 and 1.5.0.

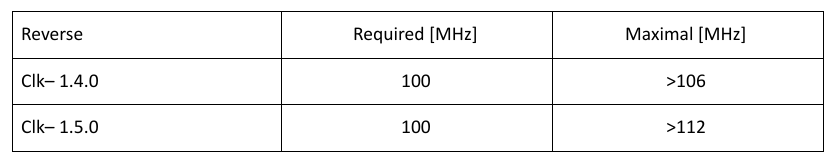

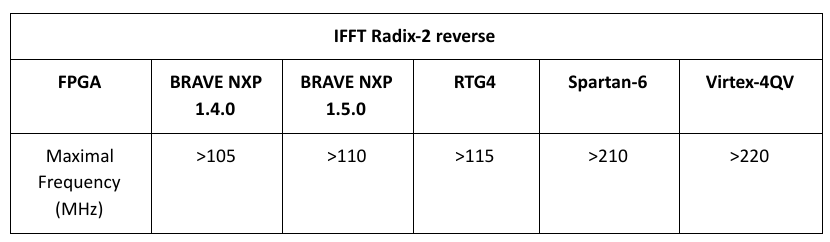

Table 2: Maximum clock speed after simulations with reversed timing optimisations, comparison between NanoXPython 1.4.0 and 1.5.0.

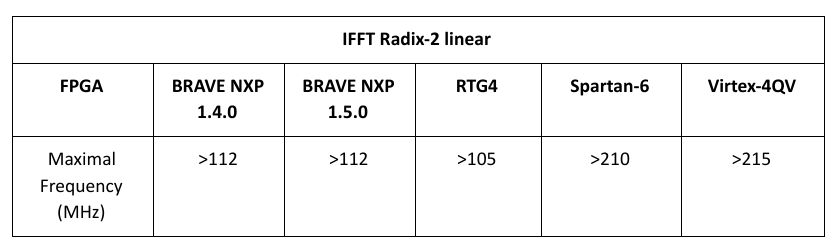

Table 3: Maximum clock speed after simulations with different architectures, linear timing, IFFT Radix-2 linear

Table 4: Maximum clock speed after simulations with different architectures, reverse timing, IFFT Radix-2 reverse

Deliverable WP1_D1.8:

An Airbus-proprietary existing design of a GNSS receiver, based on an AGGA-4 processor, was tested. Since the original design was far too large for the BRAVE, it was split into two parts and only the most important blocks were taken and tested.

Table 5: AGGA-4 Part 1 timing results with NanoXPython 1.4.0 and 1.5.0.

Table 6: AGGA-4 Part 2 timing results (ExtClk, one channel) with NanoXPython 1.4.0 and 1.5.0.

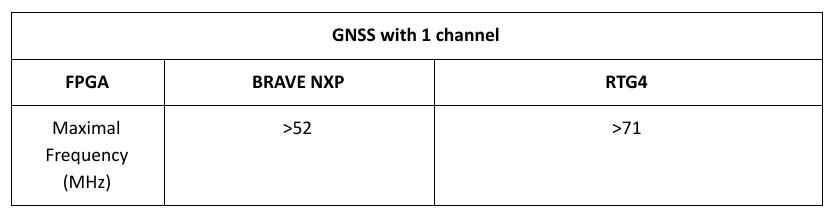

Table 7: Comparison of results obtained with GNSS 1 channel between BRAVE and RTG4, GNSS with 1 channel

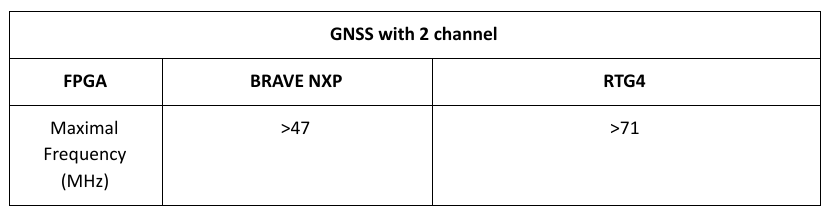

Table 8: Comparison of results obtained with GNSS 2 channel between BRAVE and RTG4, GNSS with 2 channels

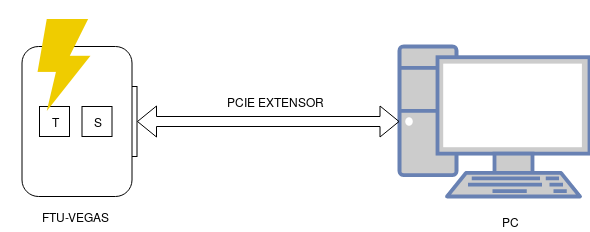

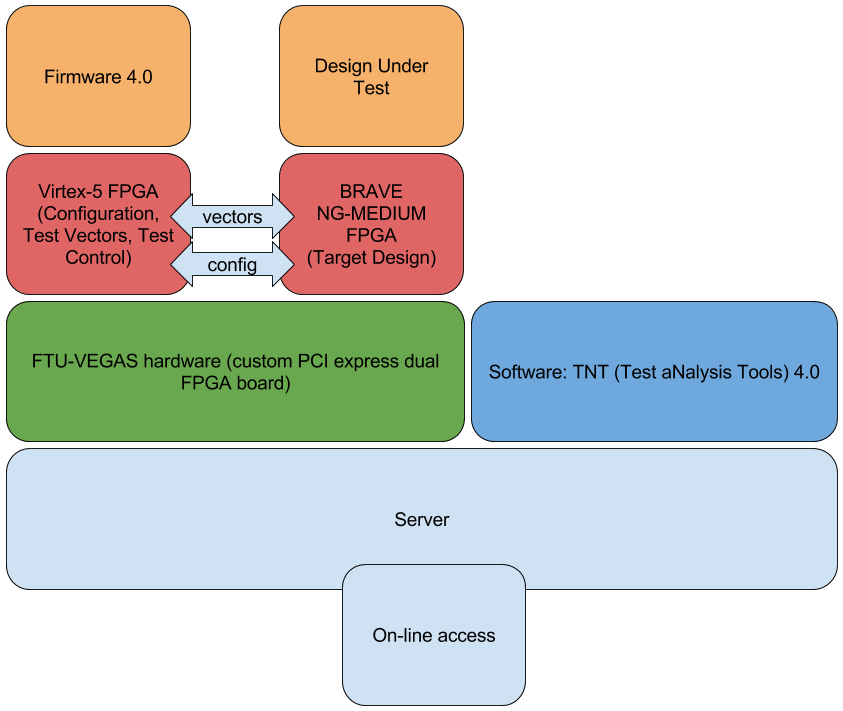

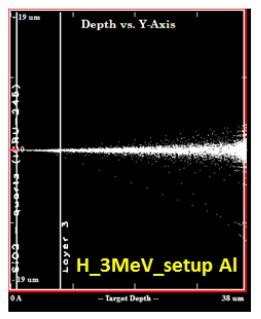

Universidad de Sevilla has developed a fault injection platform for the BRAVE FPGA, called the FTU-VEGAS. This platform is of interest for researchers and designers, in order to study design robustness in FPGAs, find optimal selective hardening schemas, and explore the possibility of using the NG-MEDIUM FPGAs in harsher-than space scenarios.

By using a PCIexpress extension cable, the platform can also be used in radiation experiments, in which it operates just controlling the target FPGA and the input/output test vectors, leaving the error insertion to the radiation beam.

The separation between the target FPGA (NG-MEDIUM) and the service FPGA allows to have a dedicated FPGA for the needed test shell circuitry, which leaves the complete target FPGA for the Design Under Test, avoiding design instrumentations that could introduce unexpected changes in the design. The software supports multiple hardware or virtual devices running in parallel, to speed-up the fault injection campaigns.

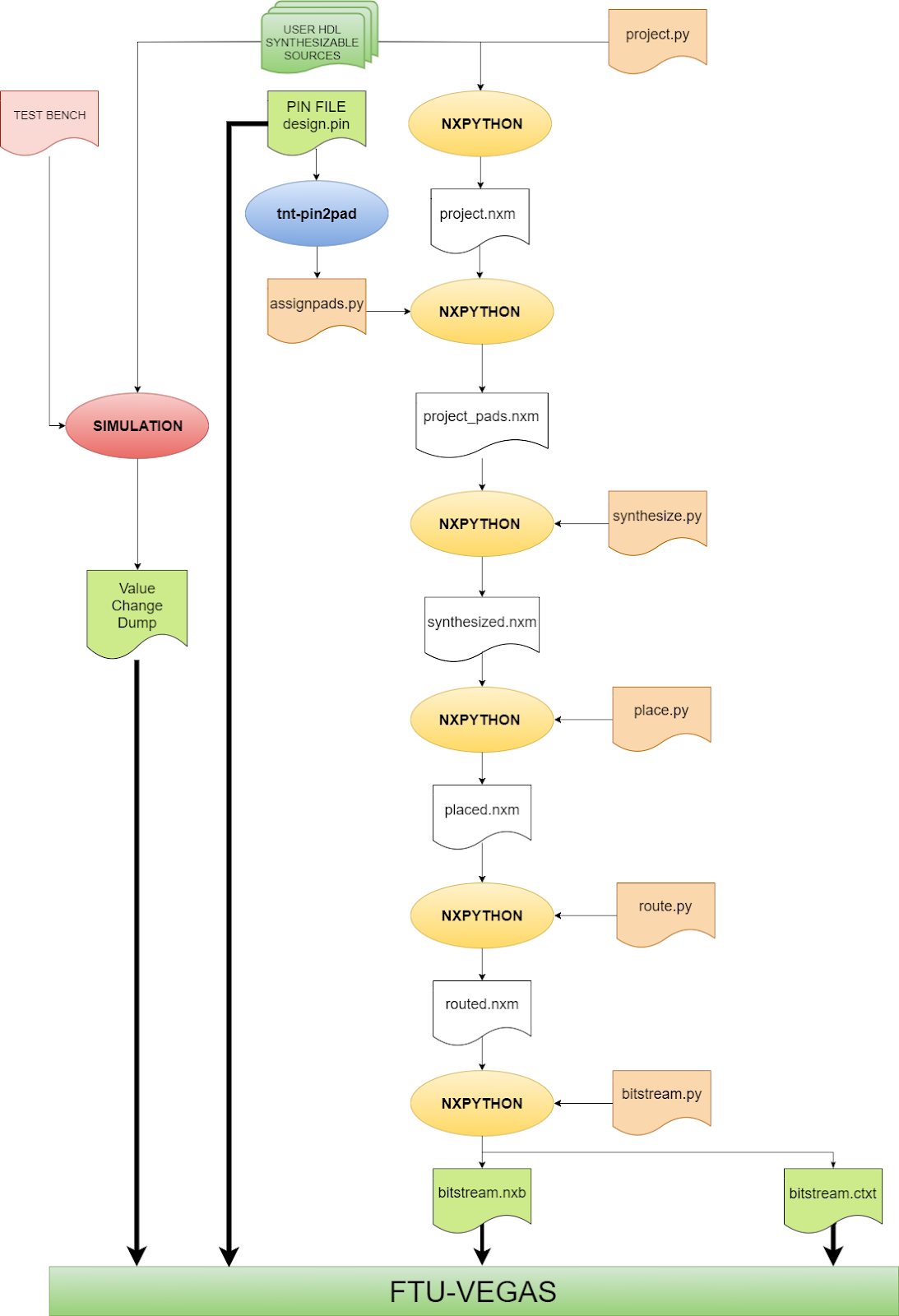

The FTU-VEGAS workflow uses tools from USE and NX. For maximum compatibility, test vectors are read in VCD format, which is an industry standard.

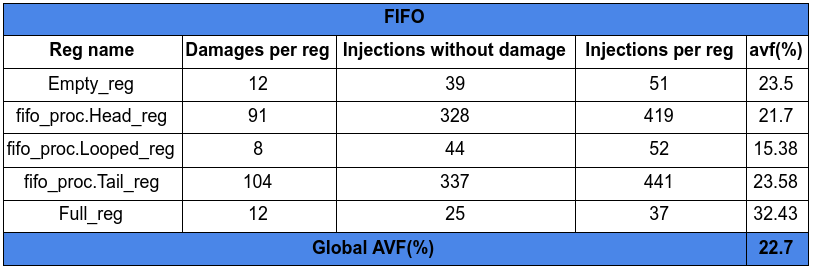

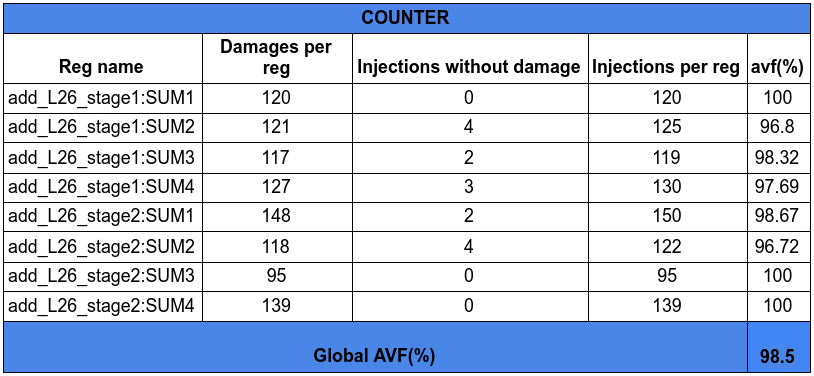

Results of the platform for some designs can be found below. In the tables, injections refer to the injected faults (which model bit upsets due to radiation effects), where damages are the errors found at the circuit outputs.

The European Space Agency has already shown interest in this platform.

Evaluation of the radiative testing capabilities of USE-CNA

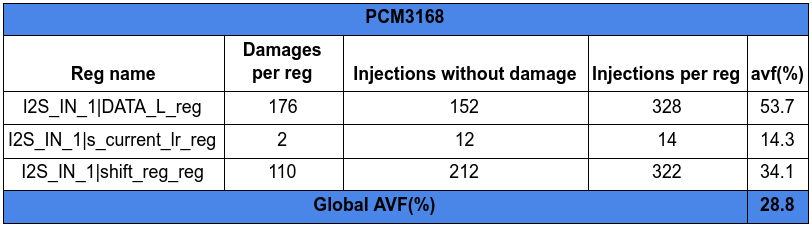

The capabilities of USE-CNA (Centro Nacional de Aceleradores) have been analyzed, both for SEE and TID. For TID, CNA's RadLab facility can be used. Also low-energy SEE (around 18 MeV) can be obtained, for pretesting and research.

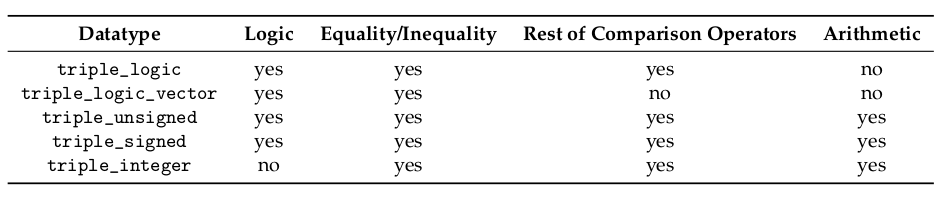

USE has also developed the triple-logic VHDL package, an open-source package to implement fine-grain selective mitigations on a design, just by changing the datatype of the object (signal, port or variable). This package is the perfect complement for a fault injection platform, since the fault injection campaigns will identify the most sensitive elements in the design, which can then be easily hardened using the package.

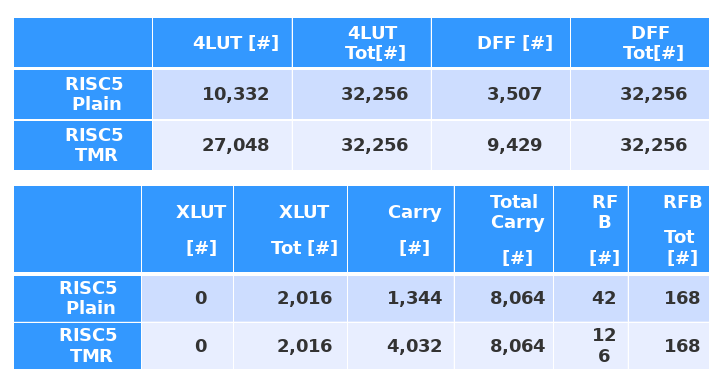

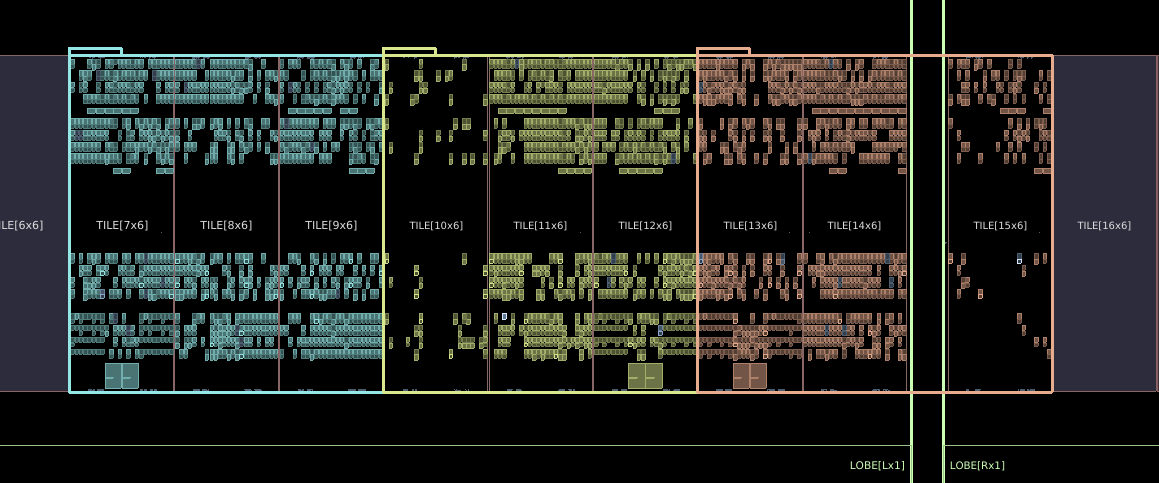

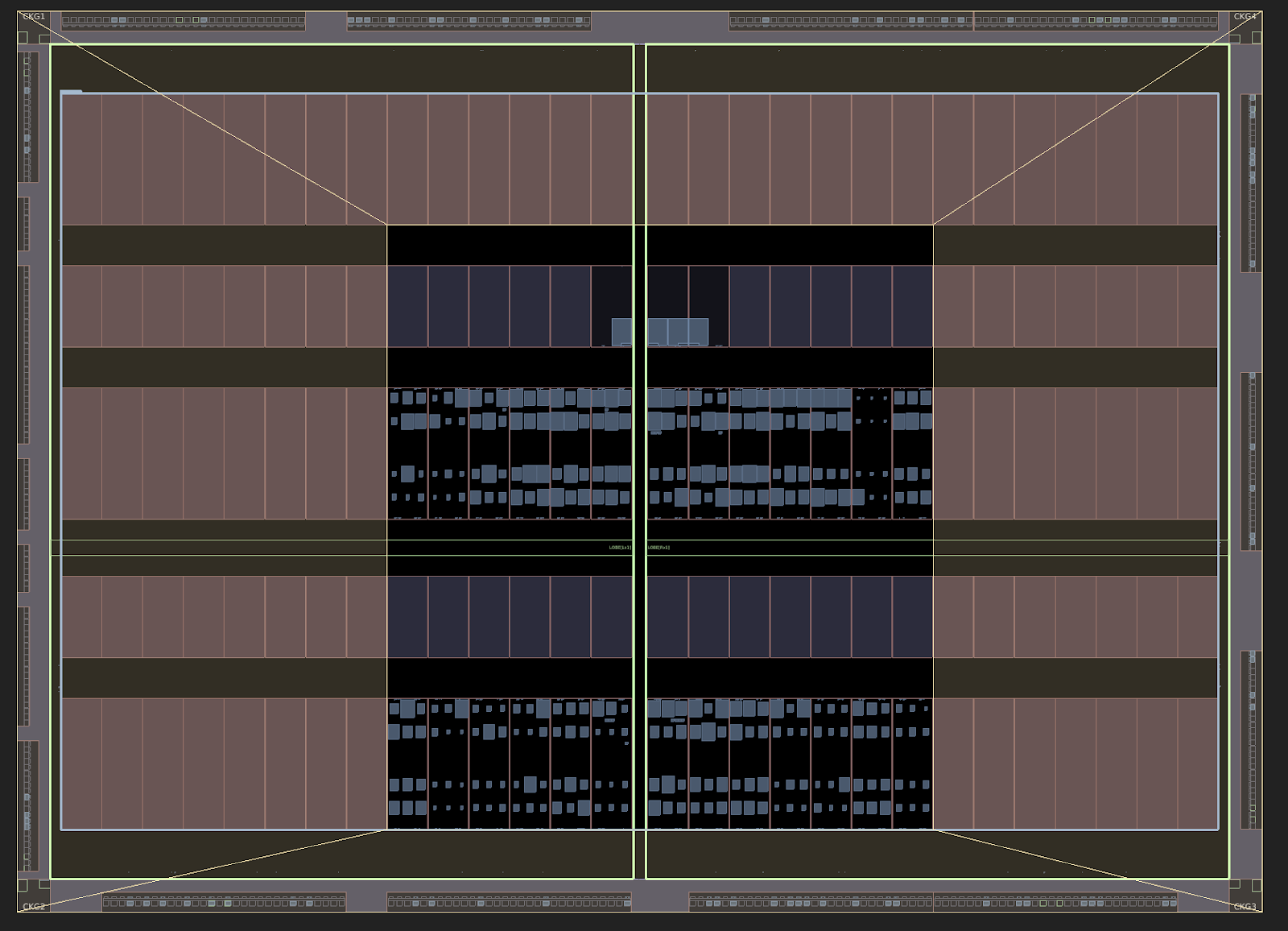

Politecnico di Torino has developed an adaptation of its static analysis & routing Veriplace tool to the NG-MEDIUM FPGA.

This tool allows to separate redundancy domains to assure that a single error in the FPGA configuration plane will not propagate simultaneously to more than one redundancy domain, for example, in the case of a short-circuit in a switching matrix.

Plain

TMR

VEGAS project has received funding from the European Union's Horizon

2020 research and innovation programme under grant

agreement N° 687220

VEGAS project has received funding from the European Union's Horizon

2020 research and innovation programme under grant

agreement N° 687220