The FTU-VEGAS firmware and software have undergone a complex verification process, which has merited its own publication.

The paper proposes a SW-VHDL co-verification methodology that bridges the efforts/results gap between ad-hoc testbenches and complex ASIC-focused verification methodologies. The proposed methodology can achieve high results of code coverage and can be deployed by using open-source tools.

The paper has been recently published in the Open Access Journal Electronics, Editorial MDPI.

For more information you can read the paper, which is freely available in Open Access here.

The system logic developed by USE for the FTU-VEGAS platform is so powerful that, by itself, it can be fully simulated, so it can be used as a simulation-based fault injection tool.

Fault injection capabilities have been added to the FPGA firmware, in order to construct a virtual device that is fully compatible with the software part of the system. Since the software supports multi-device campaigns, multiple virtual devices may be instanced in order to speed-up simulation-based fault injection campaigns.

USE has written a paper about this that has been recently published in the Open Access Journal Electronics, Editorial MDPI.

The paper is freely available in Open Access here.

The final review meeting for the VEGAS project was held online on November 19th, 2020

The agenda of the day was as follows:

10.00 – 10.30: Project update (NX)

10.30 – 11.15: WP1 overview

11.15 – 12.00: WP2 overview

12.30 – 13.30: Lunch

13.30 – 14.45: WP3 overview

14.45 – 15:30: WP4 overview

15.30 – 16:15: WP5 overview

16.15 – 16.30: Exploitation of results

16.30 – 17.00: Conclusions

The 11th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

NX's Joel LeMauff will impart the webinar: “Introducing NanoXplore and its European FPGA’s ITAR free: New perspective of the NX product roadmap fully dedicated to Space.”, on the 17 Jul 2020, under DoeEEEt.com, with support from Alter Technology.

The 10th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

Due to the COVID-19 situation, all conferences & workshops related to the project have been canceled.

The 9th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

USE's abstract "Harsher-than-space: Fault injection and user-based RHBD in the age of rad-tolerant and rad-hard devices" has been accepted to be presented at the next SpacE FPGA Users Workshop (SEFUW), at ESA/ESTEC, Noordwijk, The Netherlands, from the 17th to the 19th of March 2020.

This workshop is organized by ESA (European Space Agency) and CNES (Centre National d'Etudes Spatiales)

Politecnico di Torino has done the following presentation at the 14th HiPEAC Workshop on Reconfigurable Computing (WRC'2020), presenting the work done in the project

The name of the presentation was: “Performance and Reliabillity of Reconfigurable High Density Rad-Hard FPGAs for Space", January 20th, 2020, Bologna, Italy.

Due to the success of the previous events, the BRAVE FPGA Day are now BRAVE FPGA Days

The 3rd BRAVE FPGA Days will take place at ESTEC, Europen Space Agency, Noordwijk, The Netherlands, during the 26th and 27th of November 2019. The event has been organized by NX and ESA.

The agenda of the days is as follows:

NX has made a presentation at the ACCEDE Workshop on COTS Components for Space Applications (ACCEDE-COTS2019), Sevilla, Spain, which took place from the 6th to the 8th of November, 2019.

The presentation name is: "Why use COTS when Low-cost RH devices are available?”

The 8th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

NX will make a presentation at the 32nd MicroElectronics WorkShop (MEWS) at JAXA, Tsukuba, Japan. The event will take place on the 23rd and 24th of October 2019.

The presentation title is: “From e-FPGA cores to RHBD SoC-FPGA devices.”

Nanoxplore has a booth at RADECS 2019, Montpellier, France. Please come and check it out!

The journal paper from Universidad de Sevilla about the triple_logic VHDL package has been featured as a chapter of the Open Access book, "Radiation Tolerant Electronics"

Editor: Paul Leroux

Publisher: MDPI

ISBN: 978-3-03921-279-8 (Paperback); 978-3-03921-280-4 (PDF)

You can freely read the book on Open Acess here.

The 7th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

NanoXplore has a booth at the Single Event Effects (SEE) Symposium & Military and Aerospace Programmable Logic Devices (MAPLD) Combined Workshop, in San Diego, California, USA.

If you are nearby, please go and check it out between the 20th and the 23rd of May!

The 6th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

NX has made a presentation at the 2019 European Space Components Conference (ESCCON) (Noordwijk, NL), 11 to 13 March 2019.

The presentation name is: "NX RHBD FPGA solutions for today and tomorrow Spaceborne applications.”

NX has a booth and a presentation at the 2019 European Workshop on On-Board Data Processing (OBDP), Noodwijk, NL, which takes places from 25 to 27 February 2019. Please check them out!

The name of the presentation is: “NX RHBD FPGA solutions for OBDP applications.”

TAS-F has made a presentation at COMET IRE at ISAE, Toulouse, France. 24th January 2019.

In this event, TAS-F has presented their own experiences around the NanoXmap tool V2: maturity, work performed, implementation issues, results achieved, encountered problems and expectations.

The 5th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

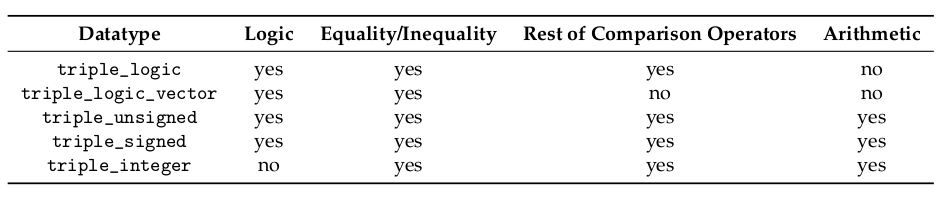

The VHDL package for fine-grain circuit hardening was published in the Open Access journal Electronics from the publisher MDPI. In the article, synthesis results from NanoXplore’s NXmap synthesizer, Xilinx’s XST and Synopsys’ Synplify are compared side-by-side. From a dissemination standpoint, it is interesting that the devices and tools begin to be known also in the academic circles.

In comparison with expensive proprietary tools, the availability of a readily-available open-source permissively-licensed solution will help lower the entry barrier for these NX customers, which is interesting for future exploitation.

The paper is freely available in Open Access here. The paper has been published online last december but is officially included in the first 2019 issue of the Journal.

NanoXplore has made the presentation “Presentation of European Rad-Hard FPGA family developed by NX under EU funding.” at RU seminar (Moscow, RU). 11DEC18. 1-day NX presentations.

A VHDL package for fine-grain circuit hardening by substituting datatypes has been developed (by USE) and released with a permissive open source license. The package works with different synthesizers and has also been tested with NXpar.

The availability of extra hardening techniques for the NG-MEDIUM can be interesting for the small percentage of users that need their devices to correctly perform in harsher-than-space environments.

You can find the VHDL package source here

The 2nd BRAVE FPGA Day has taken place at ESTEC, European Space Agency, Noordwijk, The Netherlands. 19 November 2018. This event has been organized by NX and ESA.

The agenda of the day was as follows:

The 4th NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

NanoXplore has a booth in RADECS 2018 (Goteborg, SW). Please come and check the latest news and products!

From the 18th to the 20th of September.

AD-G has published a conference paper with the results of the Master’s Thesis they worked on with Technische Universität München

Article name: “THE USE OF DIFFERENT ARCHITECTURES AND STREAK OBSERVATIONS ALGORITHMS TO DETECT SPACE DEBRIS”.

Authors: Gerard Vives Vallduriola, Tim Helfers, Franz Biersack, Steffen Linssen, Dr. Jens Utzmann, Alessandro Vananti.

Conference: ESA On-Board Processing and Data Compression 2018, Matera, Italy. September 2018.

AD-G has worked on a Master’s Thesis with Technische Universität München (TUM) using the NX FPGA and its software tools

Thesis name: Implementation of an Image Processing Algorithm for new Space Technology

Author: Franz BIERSACK

Directors: Prof. Dr. Walter STECHELE, Prof. Dr. Andreas Herkersdorf. Technische Universität München (TUM).

The 3rd NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

The VEGAS Project article has been chosen as the featured article in IETTN’s newsletter!

This means it has been deemed one of the best technology transfer & industry collaboration news of this quarter.

NanoXplore will be present at the Military and Aerospace Programmable Logic Devices (MAPLD) Workshop , with a presentation (“New RHBD FPGA vendor for Spaceborne applications – Product roadmap & 1st radiation results.”), a poster and a booth.

Please check them out between the 21st and the 24th of May.

The 2nd NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

As part of the dissemination activities carried out for the project, two presentations were made at the SpacE FPGA Users Workshop (SEFUW) that took place on the European Space Research and Technology Centre (ESTEC) of the European Space Agency (ESA). This workshop is jointly organized between ESA and CNES (Centre National d'Etudes Spatiales), and due to its attendants being in the space industry and having an explicit interest on the usage of FPGAs on Space Engineering projects, this is a perfect forum in which to disseminate the activities of the VEGAS project.

The FTU-VEGAS fault injection platform was described as part of the presentation “Fault injection for space: FT-Unshades2 updates, experiences and roadmap” made by Hipólito Guzmán (USE)

Joel LeMauff’s (NX) presentation at the 4th SpacE FPGA Users’ Workshop (SEFUW)

4th SpacE FPGA Users’ Workshop (SEFUW). 9th April 2018, European Space Research and Technology Centre, Noordwijk, The Netherlands.

IETTN has re-spinned the divulgative article VEGAS project: Industry and University collaboration to validate the first European SRAM FPGA for Space Applications. IETTN (Industrial Electronics Technology Transfer News) is an IEEE online magazine about technology transfer in the electronics sector, which puts into contact researchers, companies and Technology Transfer Offices.

You can find the article here

1st NX Facts Sheet is out! If you want receive it in your email and subscribe to next editions, send an email to Joel LeMauff

Answering to users’ requests, NanoXplore has started a periodic newsletter, called “NX FACTS SHEET”, which is meant to increase the information flow from the FPGA vendors to the users, and keep them updated on topics such as:

The newsletter will be sent on a quarterly basis.

A divulgative article about the VEGAS project has been written by USE and NX and published at USE’s Engineering School TTO (AICIA) website: VEGAS project: Industry and University collaboration to validate the first European SRAM FPGA for Space Applications

The BRAVE FPGA was featured in the EDN (Electrical Design News) Network magazine, in the Out-of-this-World Design blog, on January. The article was written by Rajan Bedi: BRAVE new ITAR/EAR-free space-grade FPGAs

This article is a significant achievement since the author is not a part of the consortium, which means that the BRAVE FPGA is gaining popularity. Having authors external to the VEGAS project consortium that are interested in disseminating news on the BRAVE FPGA will help to continue the dissemination of the project even after the project has ended. NanoXplore has supported the author during the preparation of the article.

The VEGAS project was mentioned in a divulgative talk by USE team member Hipólito Guzmán, La Electrónica en el Espacio: de Sputnik a Solar Orbiter (Electronics in Space: From Sputnik to Solar Orbiter). Semana de la Ciencia de Chiclana (Chiclana’s Science Week), Chiclana de la Frontera, Spain. 8 November 2017.

The European Space Agency has expressed interest in moderating a BRAVE FPGA Users Group in the future.

NanoXplore has booth at RADECS 2017, CERN, Geneva, Switzerland. 2-6 October 2017. Please come and check out the latest news!

NanoXplore will have an exhibition at RADSAGA, at CERN: "From Radiation Hardening to BRAVE FPGA Devices". Geneva, Switzerland. 5 October 2017.

NanoXplore and European Space Agency (ESA) have organized the BRAVE FPGA Day at ESTEC, European Space Agency, Noordwijk, The Netherlands. 11 September 2017.

This is a specific event for the users of the NanoXplore FPGAs where attendees can learn about the devices, software, IPs, and also share their experiences.

Airbus presentation by Gerard Vives at BRAVE FPGA Day at ESTEC, "ADS Feedback", European Space Agency, Noordwijk, The Netherlands. 11 September 2017.

TAS-F presentation by Gregory Grimonet about TAS-F experiences around the NanoXmap tool: maturity, work performed, implementation issues, results achieved, encountered problems and expectations, at BRAVE FPGA Day at ESTEC, European Space Agency, Noordwijk, The Netherlands. 11 September 2017.

NanoXplore has made a presentation at the Space Engineering & Technology Final Presentation Days, ESTEC, European Space Agency, Noordwijk, The Netherlands. 24th May 2017.

NanoXplore has made a presentation at RADFAC2017, Sevilla, Spain. RADFAC (From RADiation FACulté). RADFAC is an event organized by the RADECS Association, in which PhD works in their late stages are presented to peers in research & industry.

This is an occasion for PhD students to simultaneously achieve the objective of presenting their on-going work and meanwhile to meet various people who could be afterwards of importance for their future professional life. These people being either their peers, either experienced engineers and/or scientists.

Apart from student presentations, there are also presentations from facilities and companies, such as NX. The attendees included many members from industry and also important people inside the RADECS (Radiation Effects on Components and Systems) Association. 30th March 2017

The RADFAC event has been chaired by USE. The general chair of the event has been Prof. M. A. Aguirre, and the general co-chair has been Associate Professor Hipólito Guzmán, both of which are involved in the VEGAS project.

The official first year review was held in ESA/CNES Daumesnil office in

Paris

10.00 – 10.30: update on BRAVE (David Merodio from ESA)

10.30 – 11.30: VEGAS update and impact of BRAVE delay

11.30 – 12.30: partner presentation of their activities in VEGAS – 10

min per partner

12.30 – 13.30: launch

13.30 – 16.30: WP progress review

16.30 – 17.00: conclusion and next step

The VEGAS Project was presented in the 13th International School on the Effects of Radiation on Embedded Systems for Space Applications (SERESSA 2016) at Montreal, Canada, by both Universidad de Sevilla (USE) and Politecnico di Torino. 7th-10th November 2016.

The Official kick-off of VEGAS to be held in ESA/CNES Daumesnil office in Paris on the 4th of February

VEGAS project has received funding from the European Union's Horizon

2020 research and innovation programme under grant

agreement N° 687220

VEGAS project has received funding from the European Union's Horizon

2020 research and innovation programme under grant

agreement N° 687220